-

index.html

ABOUT ME

이름

오고은

생년월일

98.01.10

위치

경기도 용인시

연락처

010-7251-3263

이메일

qw433812@gmail.com

학력

아주대학교 (전자공학과)

PROJECTS

vga 영상처리

2025.06.03 ~ 2025.06.12 (4人 팀 프로젝트)

I2C 통신 기반 듀얼 FPGA 탁구 게임

- FPGA 기반 VGA 영상처리 시스템 구현

- 특정 색상 충돌 감지 및 물리 모델 기반 운동 시뮬레이션

- I2C 통신을 통해 2개 보드 간 공의 좌표를 공유하여 2인 게임으로 확장

systemVerilog, Python, Vivado, VGA

AXI4-Lite

2025.05.21 ~ 2025.05.25 (4人 팀 프로젝트)

AXI4-Lite 기반 SPI/I2C 통신 프로토콜 설계

- AXI4-Lite 기반의 SPI, I2C 통신 프로토콜 구현

- I2C 기반 보드 간 직렬 통신 인터페이스 설계

- Synopsys VCS, Verdi를 활용하여 검증

systemVerilog, Vivado, Synopsys VCS, Synopsys Verdi

AMBA APB

2025.04.30 - 2025.05.06 (4人 팀 프로젝트)

RISC-V AMBA Peripheral 설계

- RV32I 기반 Multi-Cycle CPU Core end-to-end 설계

- AMBA APB 프로토콜 기반 각종 Peripheral 연동, C기반 애플리케이션 설계

- UVM-lite 구조 기반 System Verilog Testbench를 활용한 Peripheral 기능 검증

systemVerilog, UVM-lite, RISC-V, AMBA APB

RISC-V

2025.04.09 - 2025.04.13 (1人 프로젝트)

RISC-V RV32I 기반 Single Cycle CPU Core 설계

- RISC-V RV32I 명령어 구조의 Single Cycle CPU 설계

- R, I, S, B, U, J 타입별 명령어 설계

- 테스트 벤치를 활용한 설계 내용 검증

verilog, systemVerilog, RISC-V, Vivado

센서 제어

2025.03.27 - 2025.03.30 (4人 프로젝트)

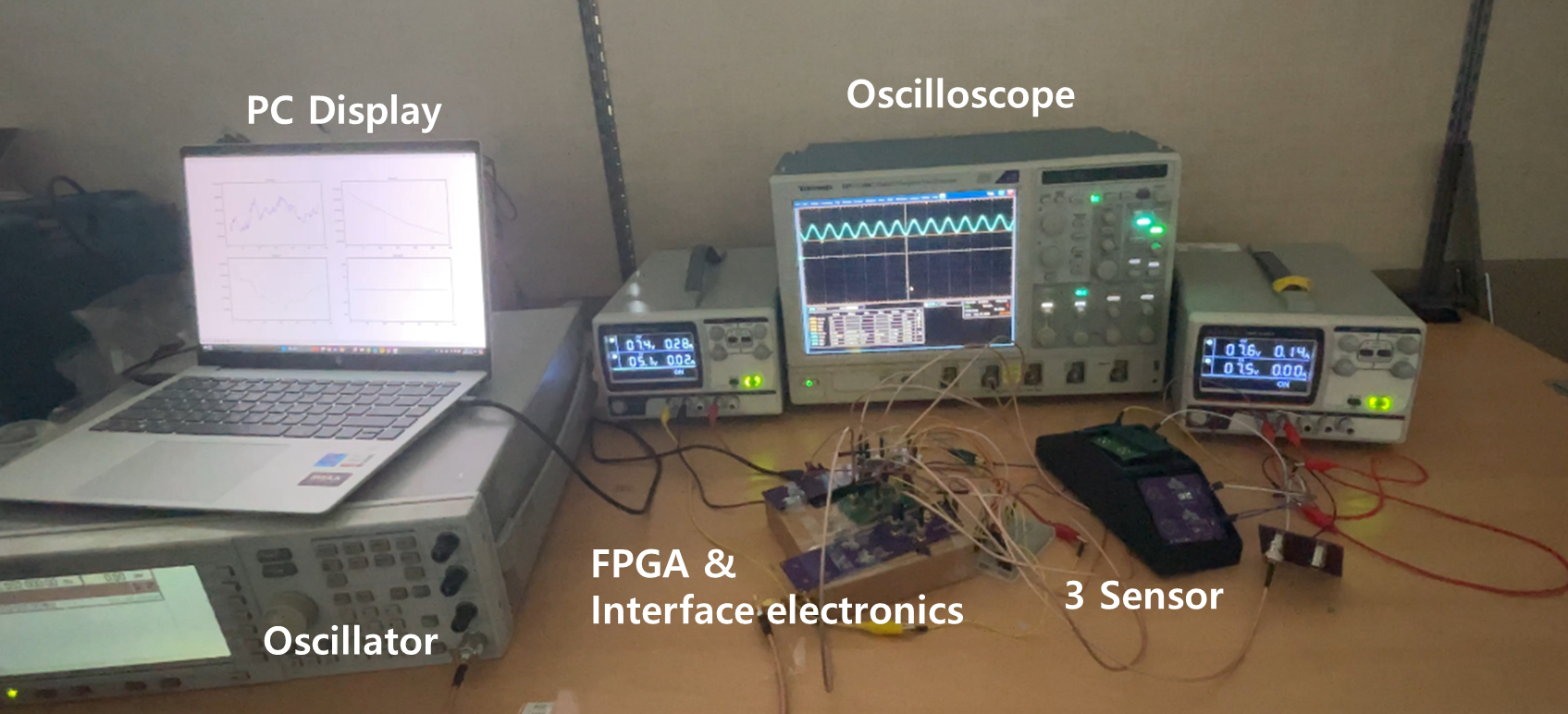

FPGA, UART 통신을 활용한 다기능 디스플레이 모듈 개발

- Basys3 FPGA 보드를 활용하여 시계, 스톱워치, 온습도 및 거리 측정 기능이 통합된 다기능 디스플레이 모듈 개발

- Basys 3 보드의 버튼과 UART RX 입력을 통한 모듈의 모드 제어

- FND, PC 화면을 통해 모듈의 출력값 표시

verilog, UART, Vivado

자동화툴 개발

2025.02.20 - 2025.02.25 (4人 프로젝트)

Python 기반의 Verilog 검증 자동화툴 개발

- Verilog로 작성된 모듈을 자동으로 검증하는 도구 개발

- Python을 활용하여 입력 값을 자동으로 생성하고, 실제 DUT의 출력과 Python 시뮬레이션의 결과가 동일한지 확인

- GIT Actions을 활용하여 테스트 모듈을 주기적으로 검사하도록 설정

verilog, Python, Github, CI/CD

센서 인터페이스 설계

2024.03 - 2024.12 (2人 프로젝트)

최종 오차 0.01% 미만의 센서 인터페이스 설계 - PCB, FPGA 로직 설계

- 코로나 방전 현상 방지를 위해 UV-C 방사를 안정적으로 감지하고 출력하는 센서 인터페이스 시스템 설계

verilog, Python, PCB, UV-C Sensor

암복호화기

2023.09 - 2023.12 (1人 개인 프로젝트)

DES/AES 암복호화기 설계

- DES(Data Encryption Standard)와 AES(Advanced Encryption Standard) 알고리즘을 기반으로 한 64-bit 암복호화기 설계

- Verilog HDL로 블록 암호 구조를 구현하고, 라운드 함수 및 키 스케줄링 구조 설계

- 파이프라인 구조 적용을 통해 초기 설계 대비 처리 속도 27% 향상

- 테스트 벤치 및 시뮬레이션을 통해 복호화 일치 여부 검증

Verilog, ModelSim

계산기

2023.03 - 2023.06 (1人 개인 프로젝트)

FPGA 계산기 설계

- FPGA 보드(Zynq 기반)를 활용한 4기능 계산기(+, -, ×, ÷) 설계

- FSM(Finite State Machine) 기반의 연산 흐름 제어 로직 구현

- 키패드 입력에 따른 상태 전이 및 연산 수행, FND 출력까지 전 과정 설계

- 각 게이트 지연 시간 설정을 통해 Setup/Hold Time 및 Glitch 현상 분석 경험

FPGA, Verilog

SKILLS

Language

Tools